# AN10900 FM+ I2C on LPC1300 Rev. 01 — 17 December 2009

Application note

#### **Document information**

| Info     | Content                                                                                                                                                                                                                                 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | LPC1300, FM+, Fast-mode Plus, I <sup>2</sup> C, Cortex-M3                                                                                                                                                                               |

| Abstract | This application note introduces how to use the Fast-mode Plus $I^2C$ of LPC1300 with demo code and an $I^2C$ demo board. NXP PCF9674 and PCA9632 are used as FM+ slave examples. $I^2C$ high speed design concerns are also discussed. |

#### **Revision history**

| Rev | Date     | Description      |

|-----|----------|------------------|

| 01  | 20091217 | Initial version. |

# **Contact information**

For additional information, please visit: <u>http://www.nxp.com</u> For sales office addresses, please send an email to: <u>salesaddresses@nxp.com</u>

AN10900\_1

Application note

# 1. Introduction

The LPC1300 is a family of ARM Cortex-M3 based microcontrollers for embedded applications featuring a high level of integration and low power consumption. Each microcontroller contains an I<sup>2</sup>C-bus interface.

This I<sup>2</sup>C-bus interface supports the full I<sup>2</sup>C-bus specification and Fast-mode Plus with a data rate of up to 1 Mbit/s. Also supported are multiple address recognition and monitor mode. In Fast-mode Plus, rates from 400 kHz to 1 MHz may be selected.

This document will give an example of how to implement Fast-mode Plus on the LPC1300 family of parts and describes  $I^2C$  high-speed design concerns.

# 2. How to implement FM+ on LPC1300

# 2.1 LPC1300 I<sup>2</sup>C Fast-mode Plus

Fast-mode Plus supports a 1 Mbit/sec transfer rate to communicate with the l<sup>2</sup>C-bus products that NXP Semiconductors is now providing.

PIO0\_4 and PIO0\_5 are the pins used for the  $I^2C$  interface. In order to use Fast-mode Plus, the I2C pins must be properly configured in the IOCONFIG register block as shown in <u>Table 1</u> and <u>Table 2</u>.

| Bit   | Symbol  | Value         | Description                               | Reset<br>value |

|-------|---------|---------------|-------------------------------------------|----------------|

| 2:0   | FUNC    |               | Selects pin function                      | 000            |

|       |         | 000           | Selects function PIO0_4                   |                |

|       |         | 001           | Selects I <sup>2</sup> C function SCL     |                |

|       |         | 010 to<br>111 | Reserved                                  |                |

| 7:3   |         | -             | Reserved                                  | 00000          |

| 9:8   | I2CMODE |               | Selects I <sup>2</sup> C mode             | 00             |

|       |         | 00            | Standard mode/ Fast-mode I <sup>2</sup> C |                |

|       |         | 01            | Fast-mode Plus I <sup>2</sup> C           |                |

|       |         | 11            | Reserved                                  |                |

| 31:10 | -       | -             | Reserved                                  | -              |

#### Table 1. IOCON\_PIO0\_4 register (IOCON\_PIO0\_4 address 0x4004 4030) bit description

Table 2. IOCON\_PIO0\_5 register (IOCON\_PIO0\_5 address 0x4004 4034) bit description

| Bit | Symbol | Value | Description             | Reset<br>value |

|-----|--------|-------|-------------------------|----------------|

| 2:0 | FUNC   |       | Selects pin function    | 000            |

|     |        | 000   | Selects function PIO0_5 |                |

| F۸ | /+ | 120 | ) or | ۱LI | PC | 130 | ) |

|----|----|-----|------|-----|----|-----|---|

ΔΝ1Λ9Λ

| Bit   | Symbol  | Value         | Description                               | Reset<br>value |

|-------|---------|---------------|-------------------------------------------|----------------|

|       |         | 001           | Selects I <sup>2</sup> C function SDA     |                |

|       |         | 010 to<br>111 | Reserved                                  |                |

| 7:3   |         | -             | Reserved                                  | 00000          |

| 9:8   | I2CMODE |               | Selects I <sup>2</sup> C mode             | 00             |

|       |         | 00            | Standard mode/ Fast-mode I <sup>2</sup> C |                |

|       |         | 01            | Fast-mode Plus I <sup>2</sup> C           |                |

|       |         | 11            | Reserved                                  |                |

| 31:10 | -       | -             | Reserved                                  | -              |

For Fast-mode Plus, FUNC(Bit 2:0) should be 001 and I2CMODE(Bit 9:8) should be 01.

After configuring Fast-mode Plus, the  $I^2C$  pins are configured with the input glitch filter enabled (this includes an open-drain output according to the  $I^2C$ -bus specification). In this mode, the pins function as high-current sinks.

#### 2.2 Example

The demo has been developed with Keil's MDK 3.70 environment and tested on an NXP LPC1300 board and an  $I^2C$  slave board. An IAR project based on EWARM 5.40 is also provided.

#### 2.2.1 Hardware

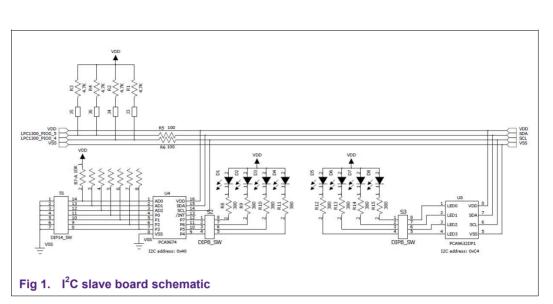

NXP's LPC1300 and an I<sup>2</sup>C FM+ demo board consist of the hardware environment. A 30cm I<sup>2</sup>C cable connects LPC1300 and I<sup>2</sup>C FM+ demo board.

The  $I^2C$  FM+ board schematic is shown in Fig 1.

The NXP PCA9674 and PCA9632 were selected as the Fast-mode Plus I<sup>2</sup>C slaves.

The PCA9674 is an NXP Remote 8-bit I/O expander for FM+  $I^2$ C-bus. In this example, P0~P3 are configured as inputs and P4~P7 are configured as outputs to drive LEDs.

The PCA9632 is an NXP 4-bit FM+  $I^2$ C-bus low power LED driver. In this example, the PCA9632 is used to drive four LEDs. The LED blink frequency is changed to show whether the  $I^2$ C-bus is in FM+ mode or standard  $I^2$ C mode.

S1.1~S1.3 are the address selectors for the PCA9674. Setting all switches to ON will configure the PCA9674 address as 0x40.

S1.4 is the mode select switch. Switch it ON to configure the  $I^2C$ -bus as FM+ mode and switch it OFF to configure the  $I^2C$ -bus to standard  $I^2C$  mode. D1~D4 are indicators for S1.4~S1.7.

LED D5~D8 are driven by the PCA9632 and are used to show the I<sup>2</sup>C mode via blinking frequency.

J3~J6 are jumpers to configure the I2C pull up resisters.

#### 2.2.2 Software

The example software is designed to demonstrate Fast-mode Plus  $I^2C$  using the LEDs. Two source code files are provided, I2C.c and I2Ctest.c.

#### 2.2.2.1 I2C.c

I2C.c contains the I<sup>2</sup>C related functions which are called by the main routine.

| Functions                            | Description                                                    |

|--------------------------------------|----------------------------------------------------------------|

| void I2C_IRQHandler(void)            | I <sup>2</sup> C interrupt handler- used for master mode only. |

| uint32_t I2CStart( void )            | Create an I <sup>2</sup> C start condition.                    |

| uint32_t I2CStop( void )             | Set the I <sup>2</sup> C stop condition.                       |

| uint32_t I2CInit( uint32_t I2cMode ) | Initialize the I <sup>2</sup> C controller.                    |

| uint32_t I2CEngine( void )           | Complete an I <sup>2</sup> C transaction from start to stop.   |

#### 2.2.2.2 I2Ctest.c

I2Ctest.c is the main routine to read and write the I<sup>2</sup>C date/command to the slaves:

```

1 while(1)

2 {

3  /* Write PCA9674 0xFF to config IOs as input and read IOs back */

4  /* Write SLA(W), data(0xFF), SLA(R), and read 2 byte back. */

```

AN10900

FM+ I2C on LPC1300

5

6

7

8 9

10

11 12

13 14

15 16

17

18

19

20

21

22

23 24

25

26 27

28

29

30

31

32 33

34 35

36 37

38

39

40

41

42 43

44

45

46

47

48 49

50

51

53 54

55

52

I2CEngine();

```

I2CWriteLength = 2;

I2CReadLength = 2;

I2CMasterBuffer[0] = PCA9674 ADDR;

I2CMasterBuffer[1] = 0xFF;

I2CMasterBuffer[2] = PCA9674 ADDR | RD BIT;

I2CEngine();

/* PCA9674 PO as switch for FM+(1Mbps) and standard/FM(400Kbps) I2C */

if (I2CSlaveBuffer[0] & 0x01)

{

/* I2C FM+ mode */

LPC IOCON->PIO0 4

&= ~0x0000031F; /* I2C FM+ I/O config */

LPC_IOCON->PIO0_4

= 0x00000101; /* I2C FM+ SCL */

LPC IOCON->PIO0 5

&= ~0x0000031F;

LPC IOCON->PIO0 5

= 0x00000101; /* I2C FM+ SDA */

/*--- Reset Baud Rate to 1Mbps ---*/

LPC I2C->SCLL = 48;//24;//0x18;

LPC I2C->SCLH = 48;//24;//0x18;

}

else

{

/* I2C standard/FM */

/* I2C I/O config */

LPC IOCON->PIO0 4

&= ~0x1F;

LPC_IOCON->PIO0_4

= 0 \times 01;

/* I2C SCL */

LPC IOCON->PIO0 5

&= ~0x1F;

/* I2C SDA */

LPC IOCON->PIO0 5

= 0 \times 01;

/*--- Reset Baud Rate to 62.5Kbps ---*/

LPC I2C->SCLL = 96;//192;//384;//2400;//0x180;

LPC I2C->SCLH = 96;//192;//384;//2400;//0x180;

}

/* Write SLA(W), data1 */

I2CWriteLength = 2;

I2CReadLength = 0;

I2CMasterBuffer[0] = PCA9674 ADDR;

I2CMasterBuffer[1] = (I2CSlaveBuffer[0] << 4) | 0x0F;</pre>

I2CEngine();

/* Write PCA9632 config parameters for LED dimming */

/* Write SLA(W), CON, OOH ~ OCh */

I2CWriteLength = 6;

I2CReadLength = 0;

I2CMasterBuffer[0] = PCA9632_ADDR;

I2CMasterBuffer[1] = 0xC2;

// Control register

I2CMasterBuffer[2] = temp;

// PWMO

I2CMasterBuffer[3] = temp + 0x40;

// PWM1

I2CMasterBuffer[4] = temp + 0x80;

// PWM2

I2CMasterBuffer[5] = temp + 0xC0;

// PWM3

```

AN10900

FM+ I2C on LPC1300

#### 2.2.3 Conditions and test results

59

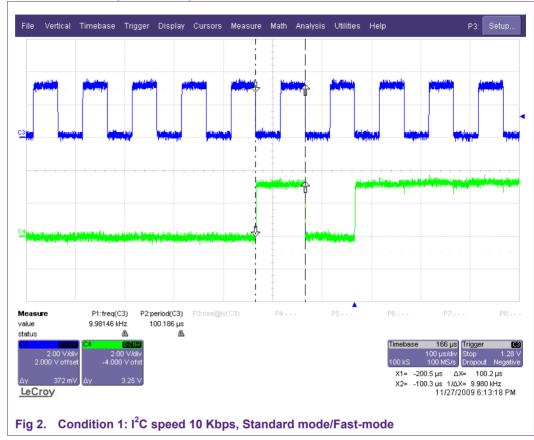

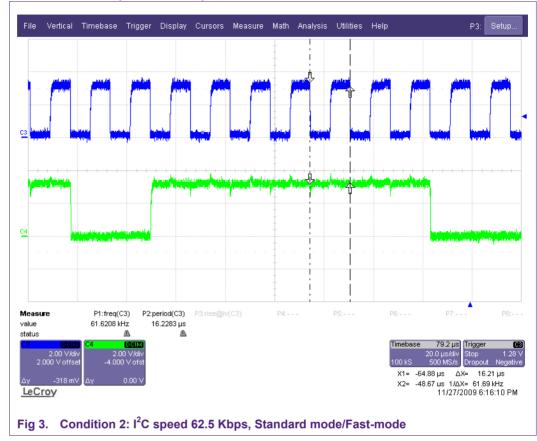

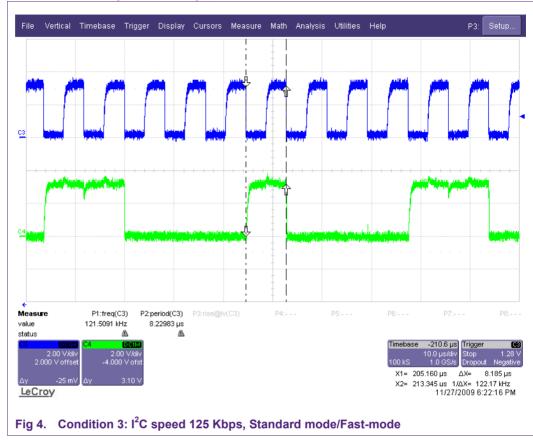

On the I<sup>2</sup>C FM+ demo board, we configure J3 and J5 closed, J4 and J6 open to select the pull up resistance as  $4.7 \text{ K}\Omega$ .

Software can set values for the registers I2SCLH and I2SCLL to select the appropriate data rate and duty cycle. I2SCLH defines the number of PCLK I2C cycles for the SCL high time; I2SCLL defines the number of PCLK\_I2C cycles for the SCL low time. The frequency is determined by the below formula (PCLK I2C is the frequency of the system clock):

$I2Cbitfrequency = \frac{PCLKI2C}{I2SCLH + I2SCLL}$

Software configures PCLKI2C as 48 MHz, and various I<sup>2</sup>C speeds are generated by different I2SCLH AND I2SCLL configurations as shown in Table 4 below:

| Condition | I <sup>2</sup> C bit frequency | I <sup>2</sup> C mode                    | PCLKI2C | I2SCLH | I2SCLL |

|-----------|--------------------------------|------------------------------------------|---------|--------|--------|

| 1         | 10 Kbps                        | Standard mode/Fast-mode I <sup>2</sup> C | 48 MHz  | 2400   | 2400   |

| 2         | 62.5 Kbps                      | Standard mode/Fast-mode I <sup>2</sup> C | 48 MHz  | 384    | 384    |

| 3         | 125 Kbps                       | Standard mode/Fast-mode I <sup>2</sup> C | 48 MHz  | 192    | 192    |

| 4         | 250 Kbps                       | Standard mode/Fast-mode I <sup>2</sup> C | 48 MHz  | 96     | 96     |

| 5         | 500 Kbps                       | Fast-mode Plus I <sup>2</sup> C          | 48 MHz  | 48     | 48     |

| 6         | 1000 Kbps                      | Fast-mode Plus I <sup>2</sup> C          | 48 MHz  | 24     | 24     |

#### I<sup>2</sup>C speed configurations Table 4.

AN10900

FM+ I2C on LPC1300

# 2.2.3.1 Condition 1: I<sup>2</sup>C speed 10 Kbps, Standard mode/Fast-mode

2.2.3.2 Condition 2: I<sup>2</sup>C speed 62.5 Kbps, Standard mode/Fast-mode

# 2.2.3.3 Condition 3: I<sup>2</sup>C speed 125 Kbps, Standard mode/Fast-mode

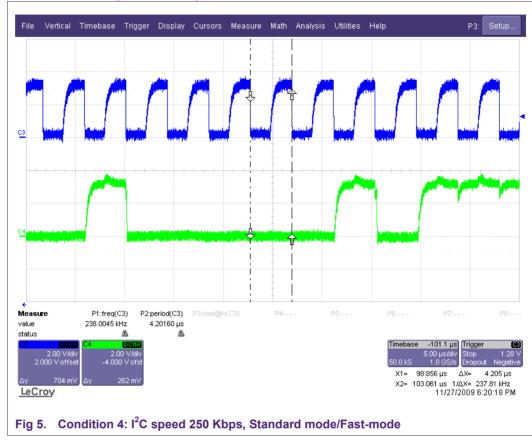

# 2.2.3.4 Condition 4: I<sup>2</sup>C speed 250 Kbps, Standard mode/Fast-mode

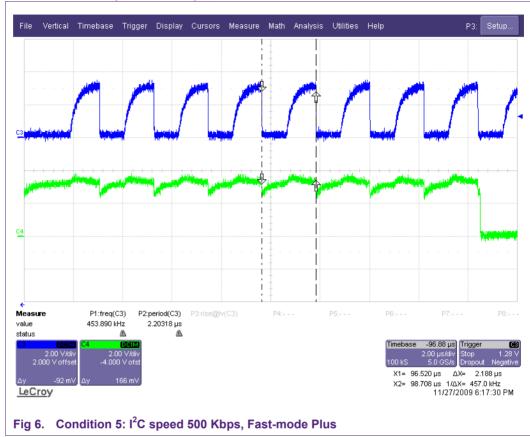

# 2.2.3.5 Condition 5: I<sup>2</sup>C speed 500 Kbps, Fast-mode Plus

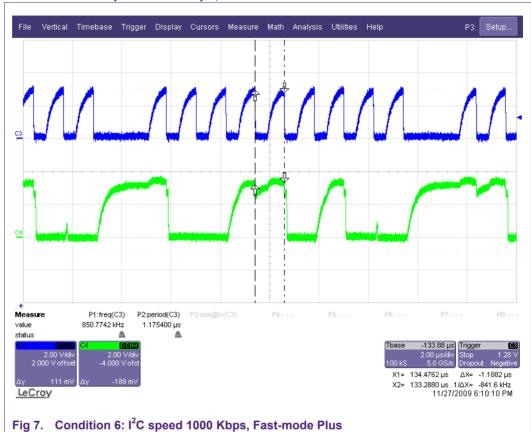

#### 2.2.3.6 Condition 6: I<sup>2</sup>C speed 1000 Kbps, Fast-mode Plus

# 3. I<sup>2</sup>C baud rate error at high speed

#### 3.1 Description

As shown in section 2.2.3 test results, the measured  $I^2C$  speed does not match the configured speed. Table 5 shows the error in each condition.

#### Table 5.I<sup>2</sup>C baud rate error

| I <sup>2</sup> C speed configured | I <sup>2</sup> C speed measured | Error    |

|-----------------------------------|---------------------------------|----------|

| 10 Kbps                           | 9.98146 Kbps                    | -0.19 %  |

| 62.5 Kbps                         | 61.6208 Kbps                    | -1.41 %  |

| 125 Kbps                          | 121.5091 Kbps                   | -2.79 %  |

| 250 Kbps                          | 238.0045 Kbps                   | -4.8 %   |

| 500 Kbps                          | 453.890 Kbps                    | -9.22 %  |

| 1000 Kbps                         | 850.7742 Kbps                   | -14.92 % |

The error becomes larger as the  $I^2C$  speed is increased. This is understood and explained here. The  $I^2C$  master monitors its own outgoing clock edges, and each clock cycle cannot start until the SCL pin returns high. Since  $I^2C$  pins are open-drain, the bus is pulled high by pull-up resistors. An  $I^2C$  slave can implement flow control by holding the

AN10900 1

clock SCL low. The master is designed to wait until the clock is released before sending the next clock.

Typically on a high-speed I<sup>2</sup>C-bus you would see a sharp high-to-low transition and a slower low-to-high transition. The asymmetry is caused by using a pull-up resistor instead of an active driver to pull up the bus.

A per-clock delay can be caused by the inherent rise time seen on the bus. Slow rise time on the SCL pin is indistinguishable from slave clock stretching. The "electrical clock stretching" delay is constant relative to the speed of the bus, but variable relative to the capacitive loading on the SCL pin. This delay would increase the clock period by a constant amount. When the I<sup>2</sup>C-bus is in a higher speed mode, this constant amount will take more share of the clock period, and make the I<sup>2</sup>C speed lower than the speed configured.

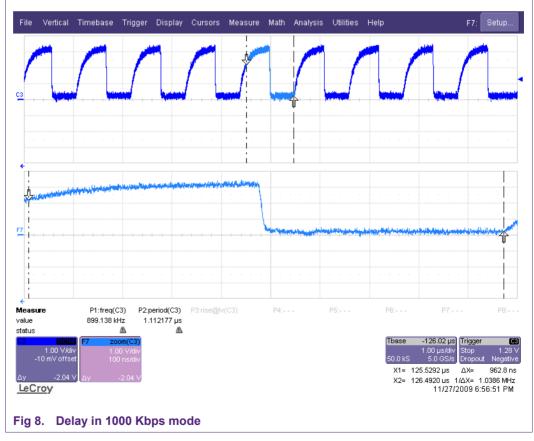

#### 3.2 Delay in 1000 Kbps mode

As an example, if in 1000 Kbps, the measured SCL frequency is 899.138 Kbps. There is a per-clock delay every SCL period.

So if the SCL period is counted from 70 %  $V_{DD}$ , as <u>Fig 8</u> shows, the SCL frequency is more accurate, around 1000 Kbps.

In a real-world system this delay cannot be completely eliminated, but can be reduced.

Because this delay is mostly the charging time of the SCL, decreasing the pull up resister could significantly reduce the delay, thus making the  $I^2C$  speed closer to the designed speed.

# 4. Conclusion

Today, a single I<sup>2</sup>C channel must support many diverse tasks simultaneously such as product authentication, EEPROM reads, temperature measurement, and power system margining. For this reason, performance has become critical. The LPC1300's integrated Fast-mode plus I<sup>2</sup>C controller provides an easy way to improve I<sup>2</sup>C-bus performance by more than 2x without adding cost or complexity. The only critical task is to make sure that the I<sup>2</sup>C-bus meets the required electrical specs such as capacitance and includes proper termination. NXP's product line includes many FM+ capable I<sup>2</sup>C devices besides the LPC1300 series microcontroller.

# 5. Legal information

### 5.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

# 5.2 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is for the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

# 5.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

I<sup>2</sup>C-bus — is a trademark of NXP B.V.

# 6. Contents

| 1.      | Introduction3                                           |

|---------|---------------------------------------------------------|

| 2.      | How to implement FM+ on LPC13003                        |

| 2.1     | LPC1300 I <sup>2</sup> C Fast-mode Plus3                |

| 2.2     | Example4                                                |

| 2.2.1   | Hardware4                                               |

| 2.2.2   | Software5                                               |

| 2.2.2.1 | l2C.c5                                                  |

| 2.2.2.2 | I2Ctest.c5                                              |

| 2.2.3   | Conditions and test results7                            |

| 2.2.3.1 | Condition 1: I <sup>2</sup> C speed 10 Kbps, Standard   |

|         | mode/Fast-mode8                                         |

| 2.2.3.2 | Condition 2: I <sup>2</sup> C speed 62.5 Kbps, Standard |

|         | mode/Fast-mode                                          |

| 2.2.3.3 | Condition 3: I <sup>2</sup> C speed 125 Kbps, Standard  |

|         | mode/Fast-mode                                          |

| 2.2.3.4 | Condition 4: I <sup>2</sup> C speed 250 Kbps, Standard  |

|         | mode/Fast-mode                                          |

| 2.2.3.5 | Condition 5: I <sup>2</sup> C speed 500 Kbps, Fast-mode |

| 2.2.3.6 | Plus                                                    |

| 2.2.3.0 | Plus                                                    |

| •       | -                                                       |

| 3.      | I <sup>2</sup> C baud rate error at high speed13        |

| 3.1     | Description                                             |

| 3.2     | Delay in 1000 Kbps mode14                               |

| 4.      | Conclusion15                                            |

| 5.      | Legal information16                                     |

| 5.1     | Definitions16                                           |

| 5.2     | Disclaimers16                                           |

| 5.3     | Trademarks16                                            |

| 6.      | Contents17                                              |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

© NXP B.V. 2009. All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, email to: salesaddresses@nxp.com

> Date of release: 17 December 2009 Document identifier: AN10900\_1